# Department of Electronics and Communication Engineering Amrita School of Engineering Amrita Vishwa Vidyapeetham M.Tech Programme in VLSI Design

#### **About Amrita**

Amrita Vishwa Vidyapeetham is a multi-disciplinary, research-intensive, private university, educating a vibrant student population of over **24,000** by **1700**+ strong faculty. Accredited with the highest possible 'A++' grade by NAAC, Amrita offers more than 250 UG, PG, and Ph.D. programs in Engineering, Management, and Medical Sciences including Ayurveda, Life Sciences, Physical Sciences, Agriculture Sciences, Arts & Humanities, and Social & Behavioral Sciences.

With seven campuses at Amaravati, Amritapuri, Bengaluru, Chennai, Coimbatore, Kochi, and Mysuru and a new upcoming campus at NCR Delhi (Faridabad) and spread over 1200+ acres with 10 million square feet of built-up space, Amrita is one of India's top-ranked private universities. Amrita has emerged as the seventh ranked university in the National Institutional Ranking Framework (NIRF) Rankings 2024.

## **About the Department**

The Department of Electronics and Communication Engineering, one of the oldest in the University, offers technology-oriented courses to create manpower in crucial areas, in line industrial expectations. The vision of the department is to mould tomorrow's technocrats, imbibing the essence of human values, for innovation and creativity in science and technology, towards building a peaceful self-sustaining nation. The department also aims at setting standards in teaching and learning for providing a bright career path for the students and to establish itself as a center of excellence in research.

#### About M.Tech Programme in VLSI Design

Very Large Scale Integrated (VLSI) Circuit Design is setting the benchmark for the growth of technology. M. Tech in VLSI Design addresses the state-of-the-art design technology using computer-aided design (CAD) tools and associated hardware. The course demands learning the principles of VLSI design and fabrication, understanding the complete design flow and developing expertise to design CMOS chips for industrial requirements. The programme lays the foundation for career opportunities in leading VLSI design industries, research labs, and reputed national and international organizations.

#### **Salient Features:**

The salient features of the programme include:

- Experienced domain-specific faculty

- Excellent infrastructure with fully equipped laboratories

- Seminars / Expert lectures / Webinars

- Industry relevant Projects

- Student publications

- Integrated M.Tech + Ph.D Programmes

- Opportunities at partner Universities abroad

- Placements and Internships

Students are exposed to various design software tools in this programme. Also, they learn to design, simulate, implement and test complex digital systems using FPGAs (Field Programmable Gate Arrays). Students are trained in several topics that cut across different domains, starting from the lowermost level of physical devices to the top level of application development. Expertise across different domains of VLSI design flow such as VLSI architecture & design, testing and verification, and device technology is a major highlight of the programme. Current focus areas include hardware security, VLSI architectures for signal processing, CAD for VLSI, high frequency CMOS design and modelling, low power VLSI and timing analysis. Ample scope exists for pursuing interdisciplinary research through collaboration and exchange programmes with various national and international institutions.

#### Vision:

The M.Tech VLSI Design program envisions producing leaders equipped with cutting-edge skills and ethical values, fostering innovation, industry collaboration, and global perspectives for sustainable advancement in integrated circuit design and technology.

#### Mission:

- To equip students with advanced technical knowledge and skills in VLSI design.

- > To promote innovation by encouraging students to come up with novel ideas and solutions.

- ➤ To enable collaboration with industry partners through Internships, industrial lectures and sharing of practical expertise.

- To cultivate a global perspective, for our students through our international partner universities by Internships, Dual degree programs and research opportunities.

**Programme Educational Objectives (PEOs)**

| PEO1 | To create manpower who have attained mastery in applying VLSI concepts to                 |

|------|-------------------------------------------------------------------------------------------|

|      | engineering problems in electronics, communication and computing so as to meet the        |

|      | needs of the industry, academia and research.                                             |

| PEO2 | To develop state-of-the-art in VLSI Design to deal with design, development,              |

|      | analysis, testing and evaluation of the critical aspects of integrated circuits and their |

|      | core concepts.                                                                            |

| PEO3 | To exhibit professional competence and leadership qualities with a harmonious             |

|      | blend of ethics, leading to the development of an integrated personality.                 |

**Programme Outcomes (POs)**

| PO1  | An ability to independently carry out research /investigation and development work to solve practical problems.                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PO2  | An ability to write and present a substantial technical report/document.                                                                                                                                                         |

| PO3  | An ability to demonstrate a degree of mastery in VLSI Design.                                                                                                                                                                    |

| PSO1 | Ability to demonstrate deep understanding of the principles, theories, and methodologies in VLSI Design, leading to specializations in Front-end design, Verification, Back-end design, Fabrication, and Advanced Architectures. |

| PSO2 | An ability to use modern tools to solve complex problems in design, development, and implementation of VLSI systems.                                                                                                             |

| PSO3 | An ability to engage in independent and life-long learning in the context of technological change and industrial demands in VLSI Design.                                                                                         |

## Curriculum

## Semester – I

| Type | Code    | Course Name                                | Teacl | hing S | Schemes | Credits |

|------|---------|--------------------------------------------|-------|--------|---------|---------|

|      |         |                                            | L     | T      | P       |         |

| FC   | 25VL601 | Semiconductor Device Modelling             | 3     | 0      | 0       | 3       |

| SC   | 25VL602 | CMOS Digital Integrated Circuits           | 3     | 0      | 0       | 3       |

| SC   | 25VL603 | Digital Circuits and Systems               | 3     | 0      | 0       | 3       |

| SC   | 25VL604 | Analog VLSI Circuits                       | 3     | 0      | 0       | 3       |

| SC   | 25VL605 | Computer Aided Design for VLSI<br>Circuits | 3     | 0      | 0       | 3       |

| SC   | 25VL681 | Analog VLSI and device modelling Lab       | 0     | 0      | 3       | 1       |

| SC | 25VL682  | RTL design and FPGA Synthesis Lab | 0  | 0 | 3  | 1   |

|----|----------|-----------------------------------|----|---|----|-----|

| HU | 22ADM501 | Glimpses of Indian Culture        | 0  | 0 | 3  | P/F |

| HU | 23HU601  | Career Competency- I              | 0  | 0 | 3  | P/F |

| HU | 25AVP501 | Mastery Over Mind (MAOM)          | 1  | 0 | 2  | 2   |

|    |          | Total                             | 16 | 0 | 11 | 19  |

## Semester – II

| Type | Code    | Course Name                                                 | Teaching Schemes |   | Credits |    |

|------|---------|-------------------------------------------------------------|------------------|---|---------|----|

|      |         |                                                             | L                | T | P       |    |

| SC   | 25VL611 | Functional Verification with Hardware Description Languages | 3                | 0 | 0       | 3  |

| SC   | 25VL612 | Digital VLSI Testing & Testability                          | 3                | 0 | 2       | 4  |

| Е    |         | Elective I                                                  |                  | 0 | 0       | 3  |

| Е    |         | Elective II                                                 |                  | 0 | 0       | 3  |

| Е    |         | Elective III                                                | 3                | 0 | 0       | 3  |

| SC   | 25VL683 | ASIC front end and back-end Design Lab                      | 0                | 0 | 3       | 1  |

| SC   | 25VL684 | Functional Verification Lab                                 | 0                | 0 | 3       | 1  |

| SC   | 25RM604 | Research Methodology 2 0                                    |                  | 0 | 2       |    |

| HU   | 23HU611 | Career Competency – II                                      |                  | 0 | 3       | 1  |

| SC   | 25VL698 | Industry Internship*                                        |                  | 0 | 2       | 1  |

|      |         | Total                                                       | 17               | 0 | 13      | 22 |

<sup>\*</sup> The internship will be during the break between the second and third semesters. This will be evaluated based on a viva-voce and a written report.

## Semester – III

| Туре | Code    | Code Course Name      |   |   | Teaching Schemes |    |  |  |

|------|---------|-----------------------|---|---|------------------|----|--|--|

|      |         |                       | L | T | P                |    |  |  |

| P    | 25VL798 | Dissertation- Phase I | 0 | 0 | 30               | 10 |  |  |

|      |         | Total                 | 0 | 0 | 30               | 10 |  |  |

## Semester-IV

|      |         |                         |     | Геасŀ   |    |    |

|------|---------|-------------------------|-----|---------|----|----|

| Type | Code    | Course Name             | mes | Credits |    |    |

|      |         |                         | L   | T       | P  |    |

| P    | 25VL799 | Dissertation – Phase II | 0   | 0       | 45 | 15 |

|      |         | Total                   |     | 0       | 45 | 15 |

**Total Credits: 66**

## **Evaluation Pattern:**

All courses will follow the evaluation pattern mandated by the university.

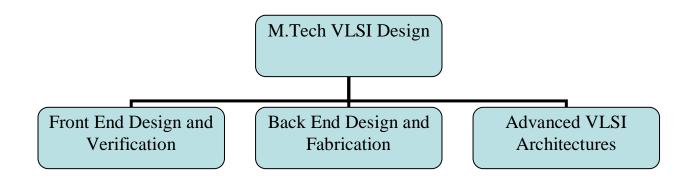

## **Elective courses:**

# Front End Design and Verification

|         | Course Name                            |    |      | Teaching |   |  |

|---------|----------------------------------------|----|------|----------|---|--|

| Code    |                                        | So | chem | es       |   |  |

|         |                                        | L  | T    | P        |   |  |

| 25VL731 | Semiconductor Memory Design            | 3  | 0    | 0        | 3 |  |

| 25VL732 | Mixed Signal VLSI Design               | 3  | 0    | 0        | 3 |  |

| 25VL733 | CMOS RF IC Design                      | 3  | 0    | 0        | 3 |  |

| 25VL734 | FPGA based System Design               | 3  | 0    | 0        | 3 |  |

| 25VL735 | Electronic System Level Design         | 3  | 0    | 0        | 3 |  |

| 25VL736 | Low Power VLSI Circuit Design          | 3  | 0    | 0        | 3 |  |

| 25VL737 | System-on-Chip & FPGA Testing          | 3  | 0    | 0        | 3 |  |

| 25VL738 | Hardware Security and Design for Trust | 3  | 0    | 0        | 3 |  |

# **Back End Design and Fabrication**

| 25VL741 | VLSI Fabrication                       | 3 | 0 | 0 | 3 |

|---------|----------------------------------------|---|---|---|---|

| 25VL742 | Physical Design                        | 3 | 0 | 0 | 3 |

| 25VL743 | Design for Manufacturability           | 3 | 0 | 0 | 3 |

| 25VL744 | Data Structures and Algorithms         | 3 | 0 | 0 | 3 |

| 25VL745 | Static Timing Analysis                 | 3 | 0 | 0 | 3 |

| 25VL746 | Machine learning for VLSI              | 3 | 0 | 0 | 3 |

| 25VL747 | MEMS Technology                        | 3 | 0 | 0 | 3 |

| 25VL748 | VLSI Packaging Technologies and Design | 3 | 0 | 0 | 3 |

## **Advanced VLSI Architectures**

| 25VL751 | VLSI Architectures for Multicore and Heterogeneous<br>Computing | 3 | 0 | 0 | 3 |

|---------|-----------------------------------------------------------------|---|---|---|---|

| 25VL752 | Reconfigurable Computing                                        | 3 | 0 | 0 | 3 |

| 25VL753 | Network on Chip                                                 | 3 | 0 | 0 | 3 |

| 25VL754 | Hardware Software Co-Design                                     | 3 | 0 | 0 | 3 |

| 25VL755 | Embedded Computing and Programming                              | 3 | 0 | 0 | 3 |

| 25VL756 | Emerging Architectures for Machine Learning                     | 3 | 0 | 0 | 3 |

| 25VL757 | Cryptography                                                    | 3 | 0 | 0 | 3 |

| 25VL758 | Internet of Things                                              | 3 | 0 | 0 | 3 |

| 25VL759 | VLSI Signal Processing                                          | 3 | 0 | 0 | 3 |

#### 25VL601

## **Semiconductor Device Modelling**

3-0-0-3

## **Course Objectives**

- Understand semiconductor fundamentals, pn junctions, and MOS structure behavior.

- Analyze two- and three-terminal MOS devices, focusing on inversion and capacitance.

- Model four-terminal MOS transistors across operating regions with practical effects.

- Study short-channel effects, develop large-signal and non-quasi-static models, and gain an overview of modern semiconductor devices.

Course Outcomes: At the end of the course, the student should be able to

- CO1: Explain the physical behavior of intrinsic and extrinsic semiconductors, pn junctions, and MOS structures under various biasing conditions.

- CO2: Analyze the characteristics of two- and three-terminal MOS devices and interpret the effects of gate voltage on device behavior.

- CO3: Model four-terminal MOS transistors considering different regions of operation, mobility variations, and temperature effects.

- CO4: Evaluate short-channel effects and develop models for scaled MOS devices, with an overview of advanced structures including SOI, Double Gate, FinFET, and GAA-FETs.

**Skills Acquired:** Ability to model and analyze semiconductor devices using physical principles and apply advanced MOSFET models for modern nano-scale device design and simulation.

## **CO-PO Mapping:**

| CO/PO | PO1 | PO2 | PO3 | PSO1 | PSO2 | PSO3 |

|-------|-----|-----|-----|------|------|------|

| CO 1  | -   | -   | -   | 3    | -    | -    |

| CO 2  | -   | -   | -   | 3    | 2    | -    |

| CO 3  | -   | -   | -   | 3    | 3    | 2    |

| CO 4  | -   | -   | -   | 3    | 3    | 2    |

## **Syllabus**

#### Unit 1:

Basics of Semiconductor – Intrinsic and Extrinsic Semiconductors, Equilibrium in absence and presence of Electric Field, Non-Equilibrium and Quasi-Fermi Levels, Charge Density. Electric Field, Potential, Poisson's Equation, Transit Time, Drift and Diffusion current, Contact Potentials, The pn Junction. Overview of the MOS Transistor – Structure, Operation and Characteristics of MOS Transistor. The Two-Terminal MOS Structures – Flatband Voltage, Potential Balance and Charge Balance, Effect of Gate-Body Voltage on Surface Condition, Accumulation and Depletion, Inversion, Small-Signal Capacitance.

#### Unit 2:

The Three-Terminal MOS Structure – Contacting the Inversion Layer, The Body Effect, Regions of Inversion, A "VCB Control" Point of View, Uses for Three-Terminal MOS Structures.

The Four-Terminal MOS Transistor - Transistor Regions of Operation, Complete All-Region Model, Simplified All-Region Models, Models Based on Quasi-Fermi Potentials, Regions of Inversion in Terms of Terminal Voltages, Strong Inversion, Weak Inversion, Moderate-Inversion and Single-Piece Models, Source-Referenced vs. Body-Referenced Modeling, Effective Mobility, Effect of Extrinsic Source and Drain Series Resistances, Temperature Effects, Breakdown, The p-Channel MOS Transistor, Enhancement-Mode and Depletion-Mode Transistors, Model Parameter Values, Model Accuracy, and Model Comparison.

#### Unit 3:

Small-Dimension Effects - Carrier Velocity Saturation, Channel Length Modulation, Charge Sharing, Drain-Induced Barrier Lowering, Punchthrough, Combining Several Small-Dimension Effects into One Model, Hot Carrier Effects and Impact Ionization, Velocity Overshoot and Ballistic Operation, Polysilicon Depletion, Quantum Mechanical Effects, DC Gate Current, Junction Leakage, Band-to-Band Tunneling and GIDL, Leakage Currents—Particular Cases, The Quest for Ever-Smaller Devices.

Large-Signal Modeling of MOS Transistor - Quasi-Static Operation, Terminal Currents in Quasi-Static Operation, Evaluation of Intrinsic Charges in Quasi-Static Operation, Transit Time under DC Conditions, Limitations of the Quasi-Static Model, Non-Quasi-Static Modeling, Extrinsic

Parasitics.

Overview of Modern Semiconductor Devices – SOI MOSFETs, Multi-gate Gate FETs like - Double Gate, FinFET, Gate All Around FETs (GAA-FETs).

#### Reference(s)

- 1. Y. Tsividis and C. McAndrew, *Operation and Modeling of the MOS Transistor*, Oxford University Press, 2011.

- 2. Donald Neamen, Dhrubes Biswas, Semiconductor Physics and Devices, McGraw Hill, 2017.

- 3. Jerry Fossum and Vishal Trivedi, "Fundamentals of Ultra thin body MOSFETs and FinFETs", Cambridge University Press, 2013.

- 4. Jean-Pierre Colinge "FinFETs and other Multi Gate Transistors", Springer (2008).

- 5. Samar K. Saha, "Compact Models for Integrated Circuit Design Conventional Transistors and Beyond", CRC Press (Taylor & Francis), 2016.

#### 25VL602

## **CMOS Digital Integrated Circuits**

3-0-0-3

#### **Course Objectives**

- To introduce the concept of MOS and CMOS logic styles.

- To comprehend the design of transistor level digital circuits.

- To enable learning different logical implementation styles.

- To impart knowledge on switch level RC delay models and data path sub systems.

**Course Outcomes:** At the end of the course, the student should be able to

- CO1: Understand/visualize the digital logic functions at device level.

- CO2: Apply suitable CMOS logical styles for the given application.

- CO3: Analyze the architecture and characterization of combinational circuits.

- CO4: Design digital CMOS circuits, subsystems and measure delay performance.

**Skills Acquired:** Design of CMOS logic circuits and performance analysis of digital architectures.

### **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | -    | -    | 2    | 2    | -    | 2    |

| CO 2  | -    | -    | 2    | 2    | 2    | 2    |

| CO 3  | -    | -    | 3    | 3    | 3    | 3    |

| CO 4  | -    | -    | 3    | 3    | 3    | 3    |

## **Syllabus**

#### Unit 1:

VLSI design flow - NMOS and PMOS Transistors— CMOS Fabrication and Layout - Threshold Voltage - MOS Transistor Theory - I-V and C-V Characteristics - Second-Order Effects - NMOS and CMOS Inverters — Pass Transistors and Transmission Gates - CMOS Combinational Logic Gates

#### Unit 2:

CMOS Transistor Characteristics - Delay Time Estimation - Switching Characteristics - CMOS Logic Structures - Mirror circuits- Pseudo nMOS logic - Clocked CMOS logic - CPL - Static CMOS Design - Dynamic CMOS Design Charge - Sharing.

#### Unit 3:

Transistor Sizing - Logical Effort - Scaling - Interconnects - Electros-Static Discharge (ESD) - Latch Up and Prevention - Datapath Subsystems - Addition/Subtraction - Comparators-One/Zero Detectors - Shifters. Sequential Circuit Design (Latches, flip-flops)- RLC Estimation - Elmore's Delay Model.

#### Reference(s)

- 1. Neil H. E. Weste and David Money Harris, *CMOS VLSI Design: A Circuits and Systems Perspective*, Fifth Edition, Addison Wesley, 2023.

- 2. Sung-Mo Kang and Yusuf Leblebici, *CMOS Digital Integrated Circuits Analysis and Design*, Fourth Edition, Tata McGraw-Hill, 2015.

- 3. Jan M. Rabaey, Anantha P. Chandrakasan and Borivoje Nikolić, *Digital Integrated Circuits: A Design Perspective*, Second Edition, Prentice Hall India, 2003.

## 25VL603

## **Digital Circuits and Systems**

3-0-0-3

## **Course Objectives**

- To understand the flow of digital design at the RTL abstraction level with HDL.

- To explore HDL approaches for modeling combinational and sequential circuits

• To introduce design of different subsystems using HDL design flow.

**Course Outcomes:** At the end of the course, the student should be able to

CO1: Ability to understand the HDL design flow and different modeling styles on hardware synthesis

CO2: Ability to develop systems at the RTL abstraction layer.

CO3: Ability to develop models for combinational and sequential blocks.

CO4: Ability to model and evaluate architectures for digital systems.

**Skills Acquired:** Design and modeling system-level architectures at the RTL abstraction level, and implementing the design with FPGA resources.

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | -    | -    | 3    | -    |      |      |

| CO 2  | -    | -    | 3    | 3    | -    |      |

| CO 3  | -    | -    | 3    | 3    | -    |      |

| CO 4  | -    | -    | 3    | 3    | 3    |      |

#### **Syllabus**

#### Unit 1:

Introduction to VLSI Design Flow and HDLs –Verilog modeling styles – Gate Level – Structural – Dataflow –RTL Abstraction –RTL Design – Design and Synthesis of Logic Circuits with Verilog HDL.

#### Unit 2:

Sequential Building Blocks - Latch, Flip-flops – Registers - Shift Registers and Digital Counters – Sequential multiplier – Finite State Machines (FSM)– Types of FSM – Design and Implementation – Capabilities and limitations of FSM –Digital Subsystem Design - FIFOs – Memories –Buffers

Fundamental mode model – Flow table – State reduction Races, Cycles and Hazards.

#### Unit 3:

Case Study of Design and Modeling of a Simple Digital System - Datapath and Controller Design - Programmable Logic Devices - CPLD - FPGA - Verilog Design for FPGA Synthesis – Introduction to High Level Synthesis.

#### Reference(s)

- 1. Michael D. Ciletti, *Advanced Digital Design with Verilog HDL*, Second Edition, Pearson Higher Education, 2011.

- 2. Stephen Brown and Zvonko Vranesic, *Fundamentals of Digital Logic with Verilog Design*, Third Edition, McGraw Hill, 2014.

- 3. Morris Mano and Michael D. Ciletti, Digital Design: *With an Introduction to the Verilog HDL*, Fifth Edition, Pearson Higher Education, 2013.

4. Peter Minns and Lan Elliott, *FSMBased Digital Design Using Verilog HDL*, Fifth Edition, John Wiley and Sons Ltd, 2008.

- 5. Scott Hauck and Andre' DeHon, "Reconfigurable Computing: The Theory and Practice of FPGA-Based Computation", Morgan Kaufmann, July 2010.

- 6. Stephen M. Trimberger, "Field programmable Gate Array Technology", Springer, 2007.

#### 25VL604

## **Analog VLSI Circuits**

3-0-0-3

### **Course Objectives**

- To provide an overview of MOS characteristics and its importance in analog design

- To introduce the design and analysis of active loaded amplifiers with and without feedback

- To provide a practical approach for the design of operational amplifiers in nanometer CMOS technology using modern engineering tools

**Course Outcomes:** At the end of the course, the student should be able to

CO1: Ability to understand MOS characteristics and to design current sources

CO2: Ability to apply techniques to design actively loaded amplifiers with and without feedback

CO3: Ability to design and analyze operational amplifiers, comparators and oscillators

CO4: Ability to analyze amplifier characteristics from top-level specifications and to model circuits using circuit simulators

**Skills Acquired:** Provides a platform to design and analyze CMOS-based active loaded amplifiers and to verify with the help of industry standard tools

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | -    | -    | 3    | 1    | 2    | 1    |

| CO 2  | -    | -    | 3    | 1    | 2    | 1    |

| CO 3  | -    | -    | 3    | -    | 2    | -    |

| CO 4  | -    | -    | 3    | 3    | 2    | 1    |

#### **Syllabus**

## Unit 1:

MOSFET: Characteristics – Biasing - Large-Signal Equivalent - Small-Signal Operation and Models - High-Frequency Modeling - Short Channel Effects. MOS Diodes - Active Resistors-Capacitors. Current Source: Cascode Current Mirrors - Gain-Boosting - Current and Voltage References - Supply Independent Biasing – Sensitivity.

## Unit 2:

Single-Stage MOS Inverters: Active Load - Current Source Load - Push-Pull Load - Small Signal Gain - Frequency Response - Miller Effect-3-dB Frequency Determination. MOS Amplifier Configurations: Common Gate - Common Drain - Cascode - Differential - Active Loaded Differential Pair. Feedback Amplifiers: Negative Feedback - Loop Gain - Oscillators - Comparators.

#### Unit 3:

Two-Stage CMOS Op-Amp Design: Gain and Frequency Response - Stability and Compensation in CMOS Op-Amps - Miller Compensated Op-Amp - Lead-Lag Compensation. Case Study of CA3130: BiMOS Operational Amplifier with MOSFET Input/CMOS Output.

#### Reference(s)

- 1. P. E. Allen and D. R. Holberg, *CMOS Analog Circuit Design*, Third Edition, Oxford Press, 2011.

- 2. B. Razavi, *Design of Analog CMOS Integrated Circuits*, Tata McGraw Hill, 2002, Reprint 2015.

- 3. P. R. Gray, P. J. Hurst, S. H. Levis and R. G. Meyer, *Analysis and Design of Analog Integrated Circuits*, Fifth Edition, Wiley Student Edition, 2009.

- 4. A S. Sedra, K. C. Smith and A. N. Chandorkar, *Microelectronic Circuits -Theory and Applications*, Seventh Edition, Oxford University Press, 2017.

#### 25VL605

## **Computer Aided Design for VLSI Circuits**

3-0-0-3

## **Course Objectives**

- To introduce physical design cycle.

- To introduce VLSI Design methodologies and provide an understanding of the VLSI design automation tools.

- To emphasize placement, floor planning and routing.

- To provide an understanding of evaluation of combinational logic synthesis.

Course Outcomes: At the end of the course, the student should be able to

CO1: Understand the VLSI physical design cycle

CO2: Apply the VLSI design automation tools

CO3: Analyze placement, floor planning and routing algorithms

CO4: Evaluate combinational logic synthesis.

**Skills Acquired:** Provide a platform for understanding and applying CAD tools for VLSI physical design.

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | -    | -    | 3    | 3    | -    | 2    |

| CO 2  | 2    | -    | 3    | 3    | 2    | 2    |

| CO 3  | 2    | -    | 3    | 3    | 2    | 2    |

| CO4   | 2    | -    | 3    | 3    | 3    | 3    |

## **Syllabus**

#### Unit 1:

VLSI Design methodologies- Introduction to VLSI design automation tools-Data structures for the representation of graphs-computational complexity- Graph algorithms - Combinatorial optimization problems-Decision problems - Complexity classes - NP-completeness and NP-hardness

#### Unit 2:

VLSI Physical Design Cycle - Placement algorithms - Partitioning-Kernighan-Lin partitioning algorithm - Terminology and floor plan representation - Optimization problems in floor planning - Types of local routing problems - Classification of compaction algorithms.

#### Unit 3:

Combinational Logic Synthesis- Binary Decision Diagrams-hardware models for high level synthesis-Allocation-Assignment and scheduling- scheduling algorithms.

#### Reference(s)

- 1. S.H. Gerez, Algorithms for VLSI Design Automation, John Wiley & Sons, 2002.

- 2. N.A. Sherwani, *Algorithms for VLSI Physical Design Automation*, Kluwer Academic Publishers, 2002.

- 3. Sadiq M. Sait, Habib Youssef, VLSI Physical Design automation: Theory and Practice, World Scientific 1999.

- 4. K. Golshan, *Physical Design Essentials: An ASIC Design Implementation Perspective*, Springer, 2010.

- 5. M. Sarrafzadeh and C.K. Wong, "An introduction to physical design", McGraw Hill.

#### 25VL681

## **Analog VLSI and Device Modelling Lab**

0-0-3-1

#### **Course Objectives**

- To understand MOS characteristics and to design and analysis of active loaded amplifiers in nanometer CMOS technology

- To understand device operation and characteristics through hands-on experiments.

- To simulate and analyze semiconductor devices like diodes, BJTs, MOSFETs, and Junctionless FETs.

Course Outcomes: At the end of the course, the student should be able to

CO1: Ability to understand MOS characteristics and to design current sources

CO2: Ability to apply techniques to design actively loaded amplifiers

CO3: Simulate and analyze the electrical characteristics of semiconductor devices.

CO4: Interpret device behavior and performance metrics under various design and biasing conditions.

**Skills Acquired:** This lab provides a platform to design and analyze CMOS-based active loaded amplifiers with the help of industry standard tools. Moreover, students will acquire skills for simulating and analyzing semiconductor devices such as diodes, BJTs, MOSFETs, and Junctionless FETs. This helps them to interpret device behavior, evaluate performance metrics, and apply semiconductor physics concepts in virtual device design and provides way for optimization.

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | -    | -    | 2    | 3    | 3    | 2    |

| CO 2  | -    | -    | 3    | 3    | 3    | 1    |

| CO 3  | -    | -    | -    | 2    | 3    | 2    |

| CO 4  | -    | -    | 1    | 3    | 3    | 1    |

#### **Syllabus**

1. For the given bias current, obtain the output and transfer characteristics of a typical 90 nm NMOS device. Determine the effect of varying (i) Drain voltage, (ii) Gate voltage, (iii) Body bias voltage and (iv) Aspect ratio. Repeat for PMOS device

2. Experimentally determine transconductance gain, threshold voltage, overdrive voltage, Early voltage, small signal input-output resistance and voltage gain of the given device for the specified bias point. Based on this, determine (i) Large-signal equivalent, (ii) Small signal equivalent, (iii) High frequency equivalent of the device and (iv)Transit frequency.

3. Construct a common-source amplifier with resistive load by setting the bias point mentioned in Expt. No.1. Based on this, (i) Observe its dc simulation, ac simulation and transient analysis, (ii) Determine the mid-band gain, 3-dB frequency, Gain-bandwidth product, and phase angle from the relevant magnitude and phase plots, (iii) Replace the resistive load by appropriate active load and observe parameters as mentioned in (i) and (ii).

Note: Active loads may be current source, diode-connected and/or push-pull types

- 4. Construct an active load differential amplifier by setting the bias point mentioned in Expt. No.1. Based on this, (i)Determine its common-mode gain and differential gain and compute its CMRR and (ii) Observe its linearity and analyze its performance trade-off.

- 5. Simulation of a PN junction diode to (i) obtain its structure, (ii) obtain diode characteristics, (iii) view contour plots and (iv) extract key device parameters through cutline analysis.

- 6. Simulation of a BJT to (i) generate the device structure, (ii) study collector current characteristics, (iii) view contour plots and (iv) extract key device parameters through cutline analysis.

- 7. Simulation of a MOSFET to (i) generate the structure, (ii) analyze drain current for varying drain voltages, (iii) view contour plots and (iv) extract key device parameters through cutline analysis.

- 8. Simulation of an SOI MOSFET to (i) simulate the device structure, (ii) examine transfer

characteristics, (iii) view contour plots, (iv) extract parameters of short channel effects like Vth, DIBL, Subthreshold slope, ION, IOFF, and ION/ IOFF and (v) extract key device parameters through cutline analysis.

9. Simulation of an SOI Junctionless FET to (i) obtain the structure, (ii) evaluate drain current behavior, (iii) view contour plots, (iv) extract parameters of short channel effects like Vth, DIBL, Subthreshold slope, ION, IOFF, and ION/ IOFF and (v) extract key device parameters through cutline analysis.

#### Reference(s)

- 1. B. Razavi, *Design of Analog CMOS Integrated Circuits*, Tata McGraw Hill, 2002, Reprint 2015.

- 2. P. E. Allen and D. R. Holberg, *CMOS Analog Circuit Design*, Third Edition, Oxford Press, 2011.

- 3. A S. Sedra, K. C. Smith and A. N. Chandorkar, *Microelectronic Circuits -Theory and Applications*, Seventh Edition, Oxford University Press, 2017.

- 4. C. K. Sarkar, *Technology Computer Aided Design Simulation for VLSI MOSFET*, 1st Edition, CRC Press, 2013.

- 5. Silvaco Inc., Atlas User's Manual, Device Simulation Software, 2018.

#### 25VL682

## **RTL Design and FPGA Synthesis Laboratory**

0-0-3-1

## **Course Objectives**

- To introduce HDL modeling, verification and simulation at RTL abstraction of combinational and sequential subsystems

- To provide understanding of FPGA Design Flow

- To provide exposure to different HDL modeling styles and their applications

- To instill background in assessing the impact of coding styles on synthesis

## **Course Outcomes (CO)**

CO1: Able to understand modeling styles

CO2: Able to apply modeling styles for realizing digital subsystems

CO3: Able to verify and analyze HDL models by writing appropriate test benches

CO4: Able to realize RTL models on FPGA platforms and evaluate the impact of coding styles on synthesis

CO5: Able to develop RTL architectures for simple digital systems

#### **CO-PO Mapping**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | -    | 2    | 3    | 3    | 3    | 2    |

| CO 2  | -    | 2    | 3    | 3    | 3    | 2    |

| CO 3  | -    | 2    | 3    | 3    | 3    | 2    |

| CO4   | -    | 2    | 3    | 3    | 3    | 2    |

| CO5   | 2    | 2    | 3    | 3    | 3    | 2    |

## **Syllabus**

- 1 Introduction to HDL simulation flow

- 2 Structural and Dataflow Modeling in Verilog

- 3 Behavioral Modeling and Verfication of combinational subsystems

- 4 Behavioral Modeling, Synthesis and FPGA implementation of combinational subsystems

- 5 Behavioral Modeling and Verfication of flip-flops, registers and counters

- 6 Behavioral Modeling and Verification of Finite State Machines

- Behavioral Modeling, Synthesis and FPGA implementation of flip-flops, registers and counters

- 8 Behavioral Modeling, Synthesis and FPGA implementation of Finite State Machines

- 9 Case Study RTL Architecture, Modeling and Verification of a Complete Digital System

- Case Study RTL Architecture Modeling, Synthesis and FPGA Implementation of a Complete Digital System

**NB**: Scripting exercises with standard tools to be included wherever appropriate.

Recommended Tools: ModelSim, Vivado

#### Reference(s)

- 1. Michael D. Ciletti, Advanced Digital Design with Verilog HDL, Second Edition, Pearson Higher Education, 2011.

- 2. Morris Mano and Michael D. Ciletti, *Digital Design: With an Introduction to the Verilog HDL*, Fifth Edition, Pearson Higher Education, 2013.

- 3. Stephen Brown and Zvonko Vranesic, Fundamentals of Digital Logic with Verilog Design, Third Edition, McGraw Hill, 2014

- 4. Peter Minns and Lan Elliott, FSM Based Digital Design Using Verilog HDL, Fifth Edition, John Wiley and Sons Ltd, 2008.

- 5. Parag K. Lala, *Principles of Modern Digital Design*, Second Edition, John Wiley and Sons Ltd., 2007.

## 23HU601 Career Competency- I 0-0-3-P/F

#### **Prerequisite:**

An open mind and the urge for self-development, basic English language skills and knowledge of high school level arithmetic.

#### **Course Objectives:**

- Help students transit from campus to corporate and enhance their soft skills

- Enable students to understand the importance of goal setting and time management skills

- Support them in developing their problem solving and reasoning skills

- Inspire students to enhance their diction, grammar and verbal reasoning skills

#### **Course Outcomes:**

- CO1: Soft Skills To develop positive mindset, communicate professionally, manage time effectively and set personal goals and achieve them.

- CO2: Soft Skills To make formal and informal presentations with self-confidence.

- CO3: Aptitude To analyze, understand and employ the most suitable methods to solve questions on arithmetic and algebra.

- CO4: Aptitude To analyze, understand and apply suitable techniques to solve questions on logical reasoning and data analysis.

CO5: Verbal - To infer the meaning of words and use them in the right context. To have a better understanding of the nuances of English grammar and become capable of applying them effectively.

CO6: Verbal - To identify the relationship between words using reasoning skills. To understand and analyze arguments and use inductive/deductive reasoning to arrive at conclusions and communicate ideas/perspectives convincingly.

## **CO-PO Mapping:**

| PO/CO | PO1 | PO2 | PO3 |

|-------|-----|-----|-----|

| CO1   | 2   | 1   | -   |

| CO2   | 2   | 1   | -   |

| CO3   | 2   | 1   | -   |

| CO4   | 2   | 1   | -   |

| CO5   | 1   | 2   | -   |

| CO6   | 2   | 2   | -   |

## **Course content:**

#### **Soft Skills:**

Introduction to 'campus to corporate transition' -

Communication and listening skills - communication process - barriers to communication - verbal and non-verbal communications - elements of effective communication - listening skills - empathetic listening - role of perception in communication.

Assertiveness skills - the concept - assertiveness and self-esteem - advantages of being assertive - assertiveness and organizational effectiveness.

Self-perception and self-confidence - locus of control (internal v/s external) - person perception - social perception - attribution theories-self presentation and impression management - the concept of self and self-confidence - how to develop self-confidence.

Goal setting - the concept - personal values and personal goals - goal setting theory - six areas of goal setting - process of goal setting - SMART goals - how to set personal goals

Time management - the value of time - setting goals/ planning and prioritizing - check the time killing habits - procrastination - tools for time management - rules for time management - strategies for effective time management

Presentation skills - the process of presentation - adult learning principles - preparation and planning - practice - delivery - effective use of voice and body language - effective use of audiovisual aids - dos and don'ts of effective presentation

Public speaking-an art - language fluency - the domain expertise (Business GK, Current affairs) - self-confidence - the audience - learning principles - body language - energy level and conviction - student presentations in teams of five with debriefing

#### Verbal:

**Vocabulary -** Familiarize students with the etymology of words - help them realize the relevance of word analysis and enable them to answer synonym and antonym questions - Create an awareness about the frequently misspelt words - commonly confused words and wrong form of words in English.

**Grammar** - Train students to understand the nuances of English Grammar and thereby enable them to spot grammatical errors and punctuation errors in sentences.

**Reasoning -** Stress the importance of understanding the relationship between words through analogy questions and learn logical reasoning through syllogism questions - Emphasize the importance of avoiding the gap (assumption) in arguments/ statements/ communication.

**Oral Communication Skills -** Aid students in using the gift of the gab to improve their debating skills.

Writing Skills - Introduce formal written communication and keep the students informed about the etiquette of email writing - Make students practice writing emails - especially composing job application emails.

#### **Aptitude:**

**Numbers -** Types - Power Cycles - Divisibility - Prime Factors & Multiples - HCF & LCM - Surds - Indices - Square roots - Cube Roots and Simplification.

**Percentage -** Basics - Profit - Loss & Discount and Simple & Compound Interest.

Ratio, Proportion & Variation - Basics - Allegations - Mixtures - Partnership.

**Averages -** Basics - Weighted Average.

**Time and Work -** Basics - Pipes & Cistern - Work Equivalence.

**Time, Speed and Distance -** Basics - Average Speed - Relative Speed - Boats & Streams - Races and Circular tracks.

**Statistics:** -Mean - Median - Mode - Range - Variance - Quartile Deviation - Standard Deviation

**Data Interpretation -** Tables - Bar Diagrams - Line Graphs - Pie Charts - Caselets - Mixed Varieties - other forms of data representation.

**Equations -** Basics - Linear - Quadratic - Equations of Higher Degree - Problems on ages.

**Logarithms, Inequalities and Modulus - Basics**

#### **Textbooks / References:**

#### **Soft Skills:**

Communication and listening skills:

- [1] Andrew J Durbin, Applied Psychology: Individual and organizational effectiveness, Pearson-Merril Prentice Hall, 2004

- [2] Michael G Aamodt, An Applied Approach, 6th edition, Wadsworth Cengage Learning, 2010 Assertiveness skills:

- [3] Robert Bolton, Dorothy Grover Bolton, People Style at Word. And Beyond: Making Bad Relationships Good and Good, Ridge Associates Inc., 2009

- [4] John Hayes Interpersonal skills at work, Routledge, 2003

- [5] Nord, W. R., Brief, A. P., Atieh, J. M., & Doherty, E. M., Meanings of occupational work: A collection of essays (pp. 21- 64), Lexington, MA: Lexington Books, 1990Self-perception and self-confidence:

- [6] Mark J Martinko, Attribution theory: an organizational perspective, St. Lucie, 1995

- [7] Miles Hewstone, Attribution Theory: Social and Functional Extensions, Blackwell,1983 Time management:

- [8] Stephen Covey, The habits of highly effective people, Free press Revised edition, 2004. [online]. Available: https://content.byui.edu/file/3dda7de4-cd79-4390-9bcf-3cb660c48dd1/1/The%207%20Habits%20of%20Highly%20Effective%20People.pdf

- [9] Kenneth H Blanchard, The 25 Best Time Management Tools & Techniques: How to Get More Done Without Driving Yourself Crazy, Peak Performance Press, 1st edition 2005

- [10] Kenneth H. Blanchard and Spencer Johnson, The One Minute Manager, William Morrow, 1984

#### Verbal:

- [11] Erica Meltzer, The Ultimate Guide to SAT Grammar

- [12] Green, Sharon, and Ira K. Wolf, Barron's New GRE, Barron's Educational Series, 2011

- [13] Jeff Kolby, Scott Thornburg & Kathleen Pierce, Nova's GRE Prep Course

- [14] Kaplan, Kaplan New GRE Premier, 2011-2012

- [15] Kaplan's GRE Comprehensive Programme

- [16] Lewis Norman, Word Power Made Easy, Goyal Publishers, Reprint edition, 1 June 2011

- [17] Manhattan Prep, GRE Verbal Strategies Effective Strategies Practice from 99th Percentile Instructors

- [18] Pearson- A Complete Manual for CAT, 2013

- [19] R.S. Aggarwal, A Modern Approach to Verbal Reasoning

- [20] S. Upendran, Know Your English, Universities Press (India) Limited, 2015

- [21] Sharon Weiner Green, Ira K. Wolf, Barron's New GRE, 19th edition (Barron's GRE), 2019

- [22] Wren & Martin, English Grammar & Composition

- [23] www.bbc.co.uk/learningenglish

- [24] www.cambridgeenglish.org

- [25] www.englishforeveryone.org

- [26] www.merriam-webster.com

#### **Aptitude:**

- [27] Arun Sharma, How to Prepare for Quantitative Aptitude for the CAT Common Admission Test, Tata Mc Graw Hills, 5th Edition, 2012

- [28] Arun Sharma, How to Prepare for Logical Reasoning for the CAT Common Admission Test, Tata Mc Graw Hills, 2nd Edition, 2014

- [29] Arun Sharma, How to Prepare for Data Interpretation for the CAT Common Admission Test, Tata Mc Graw Hills, 3rd Edition, 2015

- [30] R.S. Aggarwal, Quantitative Aptitude for Competitive Examinations, S. Chand Publishing, 2015. Online. Available: https://eltsindia.com/StudyMaterialFiles/ea007acc-bc55-4e17-8470-0d9e85313252quantitative-aptitude-for-competitive-examinations-by-rs-aggarwal-reprint-2017.pdf [31] R.S. Aggarwal, A Modern Approach to Verbal & Non-Verbal Reasoning, S. Chand Publishing, Revised-2015. Online. Available: https://vdoc.pub/documents/a-modern-approach-to-verbal-non-verbal-reasoning-3n9dee1ck6p0

- [32] Sarvesh Verma, Quantitative Aptitude-Quantum CAT, Arihant Publications, 2016

- [33] www.mbatious.com

- [34] www.campusgate.co.in

- [35] www.careerbless.com

## 25VL611 Functional Verification with Hardware Description Languages

3-0-0-3

## **Course Objectives**

- To develop a strong foundation in functional verification techniques used in ASIC/FPGA design

- To familiarize with SystemVerilog constructs for building testbenches and verification environments.

- To cultivate skills in assertion-based verification and functional coverage-driven testing

Course Outcomes: At the end of the course, the student should be able to

CO1: Understand the fundamentals of functional verification and its methodologies.

CO2: Design digital modules and corresponding testbenches using SystemVerilog

CO3: Apply effective methodologies to develop effective verification environments

CO4: Evaluate verification completeness using assertion-based techniques.

**Skills Acquired:** Creation of reusable testbenches using SystemVerilog; Verification planning and coverage closure; Application of functional coverage and assertion-based techniques.

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  |      |      | 3    | 2    |      |      |

| CO 2  |      |      | 3    | 3    | 3    | 2    |

| CO 3  |      |      | 3    | 3    | 3    | 3    |

| CO 4  |      |      | 3    | 3    | 2    | 2    |

## **Syllabus**

#### Unit 1:

Review of HDL (Verilog) –Need for functional verification - Verification lifecycle and test planning - Testbench architectures: Directed & Constraint Random - Types of coverage: Code coverage - Functional coverage - SystemVerilog for design: data types, control flow, operators - Hierarchy, modules, and connectivity

#### Unit 2:

SystemVerilog for Verification- Testbench components: tasks, functions, interfaces- Object-oriented features in SystemVerilog (classes, inheritance, polymorphism) - Constrained Random Verification-

Inter Process Communication: Threads, mailboxes and semaphores- Building verification environment with SystemVerilog

#### Unit 3:

System Verilog Assertions – immediate assertions – concurrent assertions – Boolean assertions – Sequences – properties - implication operators – nested implications – Functional Coverage: covergroups, bins, cross coverage - Coverage closure strategies and reporting – Memory Design: Behavioural Modelling and Verification environment creation – UVM – Overview, Testbench Architecture, and Component Roles

#### Reference(s)

- 1. Chris Spear and Greg Tumbush: SystemVerilog for Verification: A Guide to Learning the Testbench Language Features, 4th Edition, 2020.

- 2. Ashok B. Mehta, *Introduction to SystemVerilog: Simulation and Testbench Design*, Springer, 2021.

- 3. Janick Bergeron, Writing Testbenches Using SystemVerilog, 3rd Edition, Springer, 2016.

- 4. Ben Cohen, Srinivasan Venkataramanan, Ajeetha Kumari, Lisa Piper, *SystemVerilog Assertions Handbook: For Design and Verification*, 4th Edition, 2019.

#### 25VL612

## **Digital VLSI Testing & Testability**

3-0-2-4

#### **Course Objectives**

- To introduce the fundamentals of VLSI testing and testability.

- To impart knowledge in the development of ATPG algorithms for testing.

- To explore the concepts of DFT and BIST.

**Course Outcomes:** At the end of the course, the student should be able to

CO1: Ability to understand the concept of testing and testability in VLSI circuits.

CO2: Ability to apply test pattern generation algorithms.

CO3: Ability to analyze built-in-test concepts.

CO4: Ability to design techniques for testability in scan-based architectures

Skills Acquired: Development of testing algorithms and testable scan architectures.

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | -    | -    | 2    | -    | 2    | 2    |

| CO 2  | -    | -    | 3    | 3    | 3    | 2    |

| CO 3  | -    | -    | 3    | 2    | 3    | 2    |

| CO 4  | -    | -    | 3    | 3    | 3    | 2    |

## **Syllabus**

#### Unit 1:

Concepts of VLSI Circuit Testing - Fault Modeling - Fault Collapsing - True Value Simulation - Fault Simulation - SCOAP Testability Measures - Combinational Circuit Test Generation - Roth's D Algorithm - PODEM ATPG Algorithms.

#### Unit 2:

Sequential Circuit Test Generation – Simulation based ATPG - Test Set Compaction - NDetect ATPG - Design for Testability - Ad Hoc Techniques - Level-Sensitive Scan Design - Scan Architectures and Testing - Scan Design Rules - LFSR based Testing.

#### Unit 3:

Testable Logic Circuit Design - Logic BIST Architectures - Test Pattern Generation - Output Response Analysis - Test Stimulus Compression - Test Response Compaction - Memory BIST - RAM fault models - RAM Test Generation - Boundary Scan Architecture.

## **List of Experiments:**

- 1. Algorithms for fault list reduction

- 2. Algorithms for test pattern generation

- 3. Algorithms for fault simulation

- 4. Algorithms for computing SCOAP Testability Measures

- 5. Algorithms for test power reduction

- 6. A script to automate T-max tool flow in Synopsys

## **Reference(s)**

- 1. Vishwani D. Agrawal and Michael L. Bushnell, *Essentials of Electronic Testing for Digital Memory and Mixed Signal VLSI Circuits*, Kluwer Academic Publishers, 2000.

- 2. Parag K. Lala, *An Introduction to Logic Circuit Testing*, Morgan &Claypool Publishers, 2009.

- 3. L. T. Wang, Cheng Wen Wu and Xiaoqing Wen, *VLSI Test Principles and Architectures Design for Testability*, First Edition, Morgan Kaufmann Publishers, 2006.

- 4. Miron Abramovici, Melvin A. Breuer and Arthur D. Friedman, *Digital Systems Testing and Testable Design*, Jaico Publishing House, 2001.

#### 25VL683

#### **ASIC Frontend and Backend lab**

0-0-3-1

Course Outcomes: At the end of the course, the student should be able to

CO1: To gain understanding of the detailed steps involved in FE and BE.

CO2: Design ASIC based digital systems using industry standard EDA tools

CO3: Design, simulate and synthesize complex digital system

## **Skills Acquired:**

- ASIC based system designs using EDA tools

- Design and synthesis of complex digital systems

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  |      | 2    | 3    | 3    | 3    |      |

| CO 2  |      | 2    | 2    | 3    | 3    |      |

| CO 3  |      | 2    | 2    | 3    | 3    |      |

| CO 4  |      | 2    | 3    | 3    | 3    |      |

## **Syllabus**

A suitable low complex CUT can be considered for the entire flow.

## ASIC Frontend Flow Lab Experiments

- 1. Design of Digital Architecture for given specification (Verilog/System Verilog based RTL coding and simulation of combinational and finite state machine based design)

- 2. Logical Synthesis of Digital Architecture (RTL to Gate level Netlist)

- 3. Functional Verification (System Verilog based TB development)

- 4. Static timing Analysis (STA) ( set up/hold violation. Critical path analysis, Clock skew and uncertainty)

## ASIC Backend Flow Lab Experiments

5. Floor planning (Floor plan layout files, Placement of macros, Pin Assignment. Power ring creation)

- 6. Placement and Clock Tree Synthesis (Placement optimization, Clock tree design, skew and latency reduction)

- 7. Routing (Routing congestion, and optimization, Later assignments and via usage, Routing DRC)

- 8. Post layout Verification (DRC and LVS Check).

- 9. Power planning and IR Drop (Power mess creation, IR drop distribution)

- 10. Parasitic Extraction and Post Layout STA (parasitic modelling, crosstalk and signal integrity,

reverification after layout).

### Reference(s)

- 1. Farzad Nekoogar, Faranak Nekoogar, "From ASICs to SOCs: A Practical Approach", Pearson, 2003.

- 2. Luciano Lavagno, Louis Scheffer, and Grant Martin. *EDA for IC Implementation, Circuit Design, and ProcessTechnology (Electronic Design Automation for Integrated Circuits Handbook)*. CRC Press, Inc., USA, 2006.

- 3. EDA manuals from Synopsys and Cadence

- 4. Stuart Sutherland, "RTL Modeling With System Verilog for Simulation and Synthesis: Using System Verilog for ASIC and FPGA Design", Sutherland HDL Inc., 2017

- 5. Naveed Sherwani, "Algorithms for VLSI Physical Design Automation", Kluwer Academic Publishers in 1993.

#### 25VL684

#### **Functional Verification Lab**

0 - 0 - 3 - 1

#### **Course Objectives**

- To provide hands-on experience in functional verification of RTL designs using SystemVerilog.

- To develop skills in object-oriented programming and constrained random verification

- To create scalable verification environments using SystemVerilog interfaces,

**Course Outcomes:** At the end of the course, the student should be able to

CO1: Understand SystemVerilog RTL modeling and verification constructs

CO2: Apply object-oriented programming to create reusable testbench components

CO3: Analyze and verify DUT functionality using constrained random stimulus and interprocess communication techniques.

CO4: Design and implement complete testbenches using interface-based and layered architecture

## **Skills Acquired:**

- Design and verification of RTL modules in SystemVerilog

- Development of class-based testbenches using OOP

Exposure to practical industry-standard verification flow

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  |      | 2    | 3    | 3    | 3    |      |

| CO 2  |      | 2    | 2    | 3    | 3    |      |

| CO 3  |      | 2    | 2    | 3    | 3    |      |

| CO 4  |      | 2    | 3    | 3    | 3    | 2    |

## **Syllabus**

- 1 RTL Modeling of Combinational Circuits using SystemVerilog

- 2 RTL Modeling of Sequential Circuits using SystemVerilog

- 3 Exploration of SystemVerilog Data Types and Constructs

- 4 Design and use of interface for Structured Connectivity

- 5 Introduction to Classes and Basic Object-Oriented Programming

- 6 Advanced OOP in SystemVerilog: Inheritance and Polymorphism

- 7 Concurrency and Inter-Process Communication: Mailboxes and Semaphores

- 8 Building a Layered Testbench for an Adder/Memory Basic Driver and Stimulus

- 9 Layered Testbench with Monitors, Reference Models, and Scoreboards

- 10 Adding Assertions and Functional Coverage to SystemVerilog Testbench

- 11 Introduction to UVM: Testbench Architecture, Components, and Execution Flow

- Hands-On UVM Lab: Building a Minimal UVM Testbench for a 4-bit Counter

NB: Scripting exercises with standard tools to be included wherever appropriate.

#### Reference(s)

- 1. Chris Spear and Greg Tumbush: SystemVerilog for Verification: A Guide to Learning the Testbench Language Features (4th Edition, 2020).

- 2. Ashok B. Mehta, *Introduction to SystemVerilog: Simulation and Testbench Design* (Springer, 2021).

- 3. Janick Bergeron, Writing Testbenches Using SystemVerilog (3rd Edition, Springer, 2016).

- 4. Ben Cohen, Srinivasan Venkataramanan, Ajeetha Kumari, Lisa Piper, *SystemVerilog Assertions Handbook: For Design and Verification* (4th Edition, 2019).

#### 25RM604

## **Research Methodology**

2-0-0-2

## **Course Objectives**

• To enable defining and formulating research approaches towards obtaining solutions to practical problems.

- To facilitate development of scientific oral and written communication skills.

- To comprehend the concepts behind adhering to scientific ethics and values.

**Course Outcomes:** At the end of the course, the student should be able to

CO1: Ability to understand some basic concepts of research and its methodologies.

CO2: Ability to define and apply appropriate parameters and research problems.

CO3: Ability to develop skills to draft a research paper.

CO4: Ability to analyse and comprehend the ethical practices in conducting research and dissemination of results in different forms.

**Skills Acquired:** Design, analyse and conduct research and comprehend the results.

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | 2    | 3    | 3    | 2    | 3    | 3    |

| CO 2  | 2    | 3    | 3    | 2    | 3    | 3    |

| CO 3  | 2    | 3    | 3    | 2    | 3    | 3    |

| CO 4  | 2    | 3    | 3    | 2    | 3    | 3    |

## **Syllabus**

Meaning of Research, Types of Research, Research Process, Problem definition, Objectives of Research, Research Questions, Research design, Approaches to Research, Quantitative vs. Qualitative Approach, Understanding Theory, Building and Validating Theoretical Models, Exploratory vs. Confirmatory Research, Experimental vs Theoretical Research, Importance of reasoning in research. Problem Formulation, Understanding Modeling & Simulation, Conducting Literature Review, Referencing, Information Sources, Information Retrieval, Role of libraries in Information Retrieval, Tools for identifying literatures, Indexing and abstracting services, Citation indexes Experimental

Research: Cause effect relationship, Development of Hypothesis, Measurement Systems Analysis, Error Propagation, Validity of experiments, Statistical Design of Experiments, Field Experiments, Data/Variable Types & Classification, Data collection, Numerical and Graphical Data Analysis:

Sampling, Observation, Surveys, Inferential Statistics, and Interpretation of Results Preparation of Dissertation and Research Papers, Tables and illustrations, Guidelines for writing the abstract, introduction, methodology, results and discussion, conclusion sections of a manuscript. References, Citation and listing system of documents Intellectual property rights (IPR) - patents-copyrights- Trademarks-Industrial design geographical indication. Ethics of Research- Scientific

Misconduct- Forms of Scientific Misconduct. Plagiarism, Unscientific practices in thesis work, Ethics in science.

#### Reference(s)

- 1. Bordens, K. S. and Abbott, B. B., *Research Design and Methods A Process Approach*, 8th Edition, McGraw-Hill, 2011.

- 2. C. R. Kothari, *Research Methodology Methods and Techniques*, 2nd Edition, New Age International Publishers.

- 3. Davis, M., Davis K., and Dunagan M., Scientific Papers and Presentations, 3rdEdition, Elsevier Inc.

- 4. Michael P. Marder, Research Methods for Science, Cambridge University Press, 2011.

- 5. T. Ramappa, Intellectual Property Rights Under WTO, S. Chand, 2008.

- 6. Robert P. Merges, Peter S. Menell, Mark A. Lemley, *Intellectual Property in New Technological Age, Aspen Law & Business*, 6th Edition July 2012.

- 7. Tony Greenfield and Sue Greener, *Research Methods for Postgraduates*, 3rd Edition, John Wiley & Sons Ltd., 2016

#### 23HU611

## Career Competency II

0-0-3-1

## **Pre-Requisite:**

Willingness to learn, team spirit, basic English language and communication skills and knowledge of high school level arithmetic.

#### **Course Objectives:**

- Help students to understand the importance of interpersonal skills and teamwork

- Prepare the students for effective group discussions and interviews participation.

- Help students to sharpen their problem solving and reasoning skills

- Empower students to communicate effectively by using the correct diction, grammar and verbal reasoning skills

#### **Course Outcomes:**

- CO1: To demonstrate good interpersonal skills, solve problems and effectively participate in group discussions.

- CO2: To write technical resume and perform effectively in interviews.

- CO3: To identify, investigate and arrive at appropriate strategies to solve questions on arithmetic by managing time effectively.

- CO4: To investigate, understand and use appropriate techniques to solve questions on logical reasoning and data analysis by managing time effectively.

- C05: To be able to use diction that is more refined and appropriate and to be competent in knowledge of grammar to correct/improve sentences

- C06: To be able to examine, interpret and investigate passages and to be able to generate ideas, structure them logically and express them in a style that is comprehensible to the audience/recipient.

### **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 |

|-------|------|------|------|

| CO 1  | 2    | 2    | 1    |

| CO 2  | 2    | 2    | 1    |

| CO 3  | 2    | 2    | 1    |

| CO 4  | 2    | 2    | 1    |

| CO 5  | 1    | 1    | 2    |

| CO 6  | 2    | 2    | 2    |

#### **Course contents:**

#### **Soft Skills:**

Interpersonal skill - Ability to manage conflict - flexibility - empathetic listening - assertiveness - stress management - problem solving - understanding one's own interpersonal needs - role of effective teamwork in organizations - Group problem solving: the process - the challenges - the skills and knowledge required for the same.

Conflict management - the concept - its impact and importance in personal and professional lives (activity to identify personal style of conflict management - developing insights that help in future conflict management situations.)

Team building and working effectively in teams - the concept of groups (teams) - different stages of group formation - process of team building - group dynamics - characteristics of effective team - role of leadership in team effectiveness - (Exercise to demonstrate the process of emergence of leadership in a group, debrief and reflection) - group discussions.

Interview skills - what is the purpose of a job interview - types of job interviews - how to prepare for an interview, dos and don'ts of interview - One on one mock interview sessions with each student

#### Verbal:

**Vocabulary** - Help students understand the usage of words in different contexts. Stress the importance of using refined language through idioms and phrasal verbs.

**Grammar -** Enable students to identify poorly constructed sentences or incorrect sentences and improvise or correct them.

**Reasoning -** Facilitate the student to tap her/his reasoning skills through critical reasoning questions and logical ordering of sentences.

**Reading Comprehension -** Enlighten students on the different strategies involved in tackling reading comprehension questions.

**Public Speaking Skills -** Empower students to overcome glossophobia and speak effectively and confidently before an audience.

Writing Skills - Practice closet tests that assess basic knowledge and skills in usage and mechanics of writing such as punctuation, basic grammar and usage, sentence structure and rhetorical skills such as writing strategy, organization, and style.

#### **Aptitude:**

**Sequence and Series:** Basics, AP, GP, HP, and Special Series.

Geometry: 2D, 3D, Coordinate Geometry, Heights & Distance.

**Permutations & Combinations:** Basics, Fundamental Counting Principle, Circular Arrangements, and Derangements.

**Probability:** Basics, Addition & Multiplication Theorems, Conditional Probability and Bayes' Theorem. **Logical Reasoning:** Arrangements, Sequencing, Scheduling, Venn Diagram, Network Diagrams, Binary Logic, and Logical Connectives, Clocks, Calendars, Cubes, Non-Verbal reasoning and Symbol based reasoning.

**Logical Reasoning II:** Blood Relations, Direction Test, Syllogisms, Series, Odd man out, Coding & Decoding, Cryptarithmetic Problems and Input - Output Reasoning.

Data Sufficiency: Introduction, 5 Options Data Sufficiency and 4 Options Data Sufficiency.

**Campus recruitment papers:** Discussion of previous year's question papers of all major recruiters of Amrita Vishwa Vidyapeetham.

Miscellaneous: Interview Puzzles, Calculation Techniques and Time Management Strategies.

#### **Textbooks / References:**

#### **Soft Skills:**

#### **Team Building:**

- [1] Thomas L. Quick, Successful team building, AMACOM Div American Mgmt Assn, 1992

- [2] Brian Cole Miller, Quick Team-Building Activities for Busy Managers: 50 Exercises That Get Results in Just 15 Minutes, AMACOM; 1 edition, 2003.

- [3] Patrick Lencioni, The Five Dysfunctions of a Team: A Leadership Fable, Jossey-Bass, 1st Edition, 2002

#### Verbal:

- [4] GMAT Official Guide by the Graduate Management Admission Council, 2019

- [5] Arun Sharma, How to Prepare for Verbal Ability and Reading Comprehension For CAT

- [6] Joern Meissner, Turbocharge Your GMAT Sentence Correction Study Guide, 2012

- [7] Kaplan, Kaplan GMAT 2012 & 13

- [8] Kaplan, New GMAT Premier, Kaplan Publishing, U.K., 2013

- [9] Manhattan Prep, Critical Reasoning 6th Edition GMAT

- [10] Manhattan Prep, Sentence Correction 6th Edition GMAT

- [11] Mike Barrett SAT Prep Black Book the Most Effective SAT Strategies Ever Published

- [12] Mike Bryon, Verbal Reasoning Test Workbook Unbeatable Practice for Verbal Ability, English Usage and Interpretation and Judgement Tests

- [13] www.bristol.ac.uk/arts/skills/grammar/grammar\_tutorial/page\_55.htm

- [14] www.campusgate.co.in

## **Aptitude:**

- [15] Arun Sharma, How to Prepare for Quantitative Aptitude for the CAT Common Admission Test, Tata Mc Graw Hills, 5th Edition, 2012

- [16] Arun Sharma, How to Prepare for Logical Reasoning for the CAT Common Admission Test, Tata Mc Graw Hills, 2nd Edition, 2014

- [17] Arun Sharma, How to Prepare for Data Interpretation for the CAT Common Admission Test, Tata Mc Graw Hills, 3rd Edition, 2015

- [18] R.S. Aggarwal, Quantitative Aptitude for Competitive Examinations, S. Chand Publishing, 2015

- [19] R.S. Aggarwal, A Modern Approach to Verbal & Non-Verbal Reasoning, S. Chand Publishing, Revised -2015

- [20] Sarvesh Verma, Quantitative Aptitude-Quantum CAT, Arihant Publications, 2016

- [21] www.mbatious.com

- [22] www.campusgate.co.in

- [23] www.careerbless.com

#### 25VL698

## **Industry Internship**

0-0-2-1

## **Course Objectives:**

- To expose the students to industry setting and get acquainted with its various functions.

- To gain direct experience so as to relate and reinforce the concepts learned in the class room

- To promote collaboration between industry/Research Laboratory and the institution

#### **Course Outcomes**

- CO1: Familiarize with the industry environment/Research Laboratory

- CO2: Understand the application of theoretical concepts in a practical setting.

- CO3: Prepare technical documents/presentations related to the work completed

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | -    | -    | 3    | 2    | 3    | 3    |

| CO 2  | -    | -    | 3    | 2    | 3    | 3    |

| CO 3  | -    | 3    | 3    | 2    | 3    | 3    |

## **Syllabus**

Students have to undergo practical training in VLSI or allied industries/research laboratory of their choice with the approval of the department. At the end of the training student should submit a report and certificate of completion to the department in the prescribed format.

## 25VL798 Dissertation Phase I 0-0-30-10

## **Course Objectives**

- To enhance students' ability to conduct independent research, including literature review, data collection, and analysis.

- To foster critical analysis of existing literature and methodologies in the chosen field of study.

- To gain proficiency in selecting appropriate research methods and techniques for addressing research questions.

Course Outcomes: At the end of the course, the student should be able to

CO1: Ability to define a research problem.

CO2: Ability to apply engineering concepts to the research problem.

CO3: Ability to design and conduct independent research in the domain of interest.

CO4: Ability to evaluate and analyze the outcomes of the research.

# **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | 2    | 3    | 3    | 2    | 3    | 3    |

| CO 2  | 2    | 3    | 3    | 2    | 3    | 3    |

| CO 3  | 2    | 3    | 3    | 2    | 3    | 3    |

| CO 4  | 2    | 3    | 3    | 2    | 3    | 3    |

#### **Syllabus**

Problems and concepts may be defined based on extensive literature survey by standard research articles. Significance of proposed problem and the state-of the art to be explored. Industry relevant tools may be used for demonstrating the results with physical meaning and create necessary research components. Publications in reputed journals /conferences may be considered for authenticating the results. Prepare and submit a detailed technical report. Provide a presentation and defend the dissertation work carried out.

25VL799 Dissertation Phase II 0-0-45-15

## **Course Objectives**

- To enhance students' ability to conduct independent research, including literature review, data collection, and analysis.

- To foster critical analysis of existing literature and methodologies in the chosen field of study.

- To gain proficiency in selecting appropriate research methods and techniques for addressing research questions.

Course Outcomes: At the end of the course, the student should be able to

CO1: Ability to define a research problem.

CO2: Ability to apply engineering concepts to the research problem.

CO3: Ability to design and conduct independent research in the domain of interest.

CO4: Ability to evaluate and analyze the outcomes of the research

## **CO-PO Mapping:**

| CO/PO | PO 1 | PO 2 | PO 3 | PSO1 | PSO2 | PSO3 |

|-------|------|------|------|------|------|------|

| CO 1  | 2    | 3    | 3    | 2    | 3    | 3    |

| CO 2  | 2    | 3    | 3    | 2    | 3    | 3    |

| CO 3  | 2    | 3    | 3    | 2    | 3    | 3    |

| CO 4  | 2    | 3    | 3    | 2    | 3    | 3    |

#### **Syllabus:**

Problems and concepts may be defined based on extensive literature survey by standard research articles. Significance of proposed problem and the state-of the art to be explored. Industry relevant tools may be used for demonstrating the results with physical meaning and create necessary research components. Publications in reputed journals /conferences may be considered for authenticating the results. Prepare and submit a detailed technical report. Provide a presentation and defend the dissertation work carried out.

#### 25VL731

## **Semiconductor Memory Design**

3-0-0-3

## **Course Objectives**

To understand the architecture, operation, and applications of various semiconductor memory technologies, including SRAM, DRAM, ROM, PROM, EPROM, EEPROM, and Flash memory.

- To explore advanced memory technologies such as FRAM, MRAM, and GaAs- based memories, along with their advantages and applications.

- To study emerging memory technologies, including experimental memory devices, and their potential impact on future semiconductor memory design.

- To analyze and compare different memory architectures to optimize performance and power consumption for specific applications.

**Course Outcomes:** At the end of the course, the student should be able to

- CO1: understand the fundamental principles and working mechanisms of various memory technologies, including SRAM, DRAM, and nonvolatile memories.

- CO2: compare advanced memory technologies such as FRAM, MRAM, and experimental memory devices for their advantages and limitations.

- CO3: analyze different memory architectures and their applications in modern computing systems.

- CO4: apply knowledge of memory technologies to design and optimize memory systems for specific applications.

**Skills Acquired:** The student will acquire the ability to understand and differentiate various memory technologies, analyze memory architectures and their impact on system performance, evaluate emerging memory technologies for advanced applications, and apply memory design concepts for optimization in real-world scenarios.

## **CO-PO Mapping:**

| CO/PO | PO1 | PO2 | PO3 | PSO1 | PSO2 | PSO3 |

|-------|-----|-----|-----|------|------|------|

| CO1   | -   | -   | 3   | 3    | -    | -    |

| CO2   | -   | -   | 3   | 3    | -    | -    |

| CO3   | -   | -   | 3   | 2    | -    | -    |

| CO4   | -   | -   | 3   | 3    | -    | 2    |

## **Syllabus**

#### Unit 1:

Static Random-Access Memories (SRAMs): SRAM cell structure, MOS SRAM architectures, MOS RAM Cell and Peripheral circuit operation, Bipolar SRAM technologies, Silicon on Insulator (SOI) Technology, Advanced SRAM architectures, Application-specific SRAMs.

Dynamic Random-Access Memories (DRAMs): DRAM technology development, CMOS DRAMs, DRAM Cell Theory and Advanced cell structures, BiCMOS DRAMs, Soft-Error

failures in DRAMs, Advanced DRAM Designs and Architectures, Application-Specific DRAMs.

#### Unit 2:

Read-Only Memories (ROMs): Masked ROMs, Technology development and Cell programming, High-Density (Multimegabit) ROMs. Programmable Read-Only Memories (PROMs): Bipolar PROMs, CMOS PROMs. Erasable (UV) Programmable Read-Only Memories (EPROMs): Floating-gate EPROM cells, EPROM Technology Developments, Advanced EPROM Architectures, One-Time Programmable (OTP) EPROMs.

Electrically Erasable PROMs (EEPROMs): EEPROM technologies – MNOS, SONOS, FLOTOX, Textured-Polysilicon Technology; EEPROM architectures, nonvolatile SRAM (Shadow RAM). Flash Memories: Flash memory cells and Technology Developments, Advanced Flash Memory Architectures.

#### Unit 3:

Ferroelectric Random-Access Memories (FRAMs): Basic theory, FRAM Cell and Memory Operation, FRAM Technology Developments, comparison of FRAMs with EEPROMs.Gallium Arsenide (GaAs) FRAMs: GaAs-based FRAM technologies and applications. Analog Memories: Concepts and applications of analog memory technologies. Magnetoresistive Random Access Memories (MRAMs): MRAM technology and advancements.

Experimental Memory Devices: Quantum-Mechanical Switch Memories, GaAs n-p-n-p Thyristor/JFET Memory cell, Single-Electron Memory, Neuron-MOS Multiple-Valued (MV) Memory Technology.

#### Reference(s)

- 1. Ashok K.Sharma, *Semiconductor Memories Technology, testing and reliability*, Prentice hall of India Private Limited, New Delhi 1997.

- 2. Ashok K Sharma, Advanced Semiconductor Memories Architecture, Design and Applications, Wiley 2002.

- 3. Shimeng Yu, Semiconductor Memory Devices and Circuits, CRC Press, 2013.

#### 25VL732

## **Mixed Signal VLSI Design**

3-0-0-3

## **Course Objectives**

- To introduce the concepts of mixed signal VLSI circuits